# **FireSim Documentation**

Release 1.14.1

Sagar Karandikar, Howard Mao, Donggyu Kim, David Biancolin, Alon Amid, Berkeley Architecture Research

# **GETTING STARTED:**

| 1 | FireS                          | im Basics                                                                  | 3  |  |  |

|---|--------------------------------|----------------------------------------------------------------------------|----|--|--|

|   | 1.1                            | Three common use cases:                                                    | 3  |  |  |

|   |                                | 1.1.1 Single-Node Simulation In Parallel Using On-Premise FPGAs            | 3  |  |  |

|   |                                | 1.1.2 Single-Node Simulation In Parallel Using Cloud FPGAs                 | 3  |  |  |

|   |                                | 1.1.3 Datacenter/Cluster Simulation                                        | 4  |  |  |

|   | 1.2                            | Other Use Cases                                                            | 4  |  |  |

|   | 1.3                            | Background/Terminology                                                     | 4  |  |  |

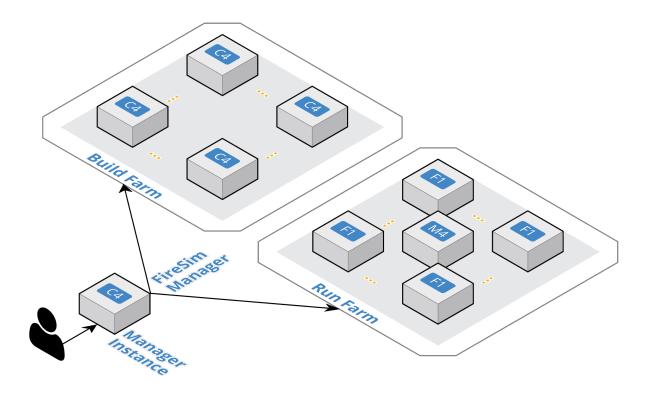

|   | 1.4                            | Using FireSim/The FireSim Workflow                                         | 5  |  |  |

| 2 | Initia                         | l Setup/Installation                                                       | 7  |  |  |

|   | 2.1                            | First-time AWS User Setup                                                  | 7  |  |  |

|   |                                | 2.1.1 Creating an AWS Account                                              | 7  |  |  |

|   |                                | 2.1.2 AWS Credit at Berkeley                                               | 7  |  |  |

|   |                                | 2.1.3 Requesting Limit Increases                                           | 7  |  |  |

|   | 2.2                            | Configuring Required Infrastructure in Your AWS Account                    | 8  |  |  |

|   |                                | 2.2.1 Select a region                                                      | 8  |  |  |

|   |                                | 2.2.2 Key Setup                                                            | 8  |  |  |

|   |                                | 2.2.3 Check your EC2 Instance Limits                                       | 8  |  |  |

|   |                                | 2.2.4 Start a t2.nano instance to run the remaining configuration commands | 9  |  |  |

|   |                                | 2.2.5 Run scripts from the t2.nano                                         | 9  |  |  |

|   |                                | 2.2.6 Terminate the t2.nano                                                | 10 |  |  |

|   |                                | 2.2.7 Subscribe to the AWS FPGA Developer AMI                              | 10 |  |  |

|   | 2.3                            | Setting up your Manager Instance                                           | 10 |  |  |

|   |                                | 2.3.1 Launching a "Manager Instance"                                       | 10 |  |  |

|   |                                | 2.3.2 Setting up the FireSim Repo                                          | 20 |  |  |

|   |                                | 2.3.3 Completing Setup Using the Manager                                   | 21 |  |  |

| 3 | Running FireSim Simulations 23 |                                                                            |    |  |  |

|   | 3.1                            | Running a Single Node Simulation                                           | 23 |  |  |

|   |                                | 3.1.1 Building target software                                             | 23 |  |  |

|   |                                | 3.1.2 Setting up the manager configuration                                 | 24 |  |  |

|   |                                | 3.1.3 Launching a Simulation!                                              | 28 |  |  |

|   | 3.2                            | Running a Cluster Simulation                                               | 33 |  |  |

|   |                                | 3.2.1 Returning to a clean configuration                                   | 33 |  |  |

|   |                                | 3.2.2 Building target software                                             | 33 |  |  |

|   |                                | 3.2.3 Setting up the manager configuration                                 | 34 |  |  |

|   |                                | 3.2.4 Launching a Simulation!                                              | 37 |  |  |

| 4 | Build                          | ing Your Own Hardware Designs (FireSim FPGA Images)                        | 45 |  |  |

|   | 4.1                            | Amazon S3 Setup                                                            | 45 |  |  |

|   |                                |                                                                            |    |  |  |

|   | 4.2<br>4.3 |           | ecipes                                                      |

|---|------------|-----------|-------------------------------------------------------------|

| 5 | Man        | ager Usas | ge (the firesim command) 47                                 |

|   | 5.1        |           | w                                                           |

|   |            | 5.1.1     | "Inputs" to the Manager                                     |

|   |            |           | Logging                                                     |

|   | 5.2        |           | r Command Line Arguments                                    |

|   |            | 5.2.1     | runtimeconfigfile FILENAME 49                               |

|   |            | 5.2.2     | buildconfigfile FILENAME                                    |

|   |            | 5.2.3     | buildrecipesconfigfile FILENAME                             |

|   |            | 5.2.4     | hwdbconfigfile FILENAME                                     |

|   |            | 5.2.5     | overrideconfigdata SECTION PARAMETER VALUE                  |

|   |            | 5.2.6     | launchtime TIMESTAMP                                        |

|   |            | 5.2.7     | TASK                                                        |

|   | 5.3        |           | r Tasks                                                     |

|   | 5.5        | 5.3.1     | firesim managerinitplatform {f1,vitis}                      |

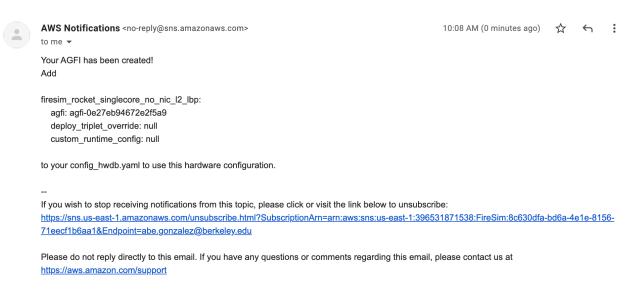

|   |            | 5.3.2     | firesim buildafi                                            |

|   |            | 5.3.3     | firesim buildbitstream                                      |

|   |            | 5.3.4     |                                                             |

|   |            |           | firesim builddriver                                         |

|   |            | 5.3.5     | firesim tar2afi                                             |

|   |            | 5.3.6     | firesim shareagfi                                           |

|   |            | 5.3.7     | firesim launchrunfarm                                       |

|   |            | 5.3.8     | firesim terminaterunfarm                                    |

|   |            | 5.3.9     | firesim infrasetup                                          |

|   |            | 5.3.10    | firesim boot                                                |

|   |            | 5.3.11    | firesim kill                                                |

|   |            | 5.3.12    | firesim runworkload                                         |

|   |            | 5.3.13    | firesim runcheck                                            |

|   | 5.4        |           | r Configuration Files                                       |

|   |            | 5.4.1     | config_runtime.yaml 57                                      |

|   |            | 5.4.2     | config_build.yaml 63                                        |

|   |            | 5.4.3     | config_build_recipes.yaml                                   |

|   |            | 5.4.4     | config_hwdb.yaml                                            |

|   |            | 5.4.5     | Run Farm Recipes (run-farm-recipes/*)                       |

|   |            | 5.4.6     | Build Farm Recipes (build-farm-recipes/*)                   |

|   |            | 5.4.7     | Bit Builder Recipes (bit-builder-recipes/*)                 |

|   | 5.5        | Manage    | r Environment Variables                                     |

|   |            | 5.5.1     | FIRESIM_RUNFARM_PREFIX                                      |

|   | 5.6        | Manage    | r Network Topology Definitions (user_topology.py) 87        |

|   |            |           | user_topology.py contents:                                  |

|   | 5.7        | AGFI M    | letadata/Tagging96                                          |

| 6 | Worl       | kloads    | 97                                                          |

|   | 6.1        | Defining  | g Custom Workloads                                          |

|   |            | 6.1.1     | Uniform Workload JSON                                       |

|   |            | 6.1.2     | Non-uniform Workload JSON (explicit job per simulated node) |

|   | 6.2        | FireMar   | shal                                                        |

|   | 6.3        |           | 017                                                         |

|   | 6.4        |           | g Fedora on FireSim                                         |

|   | 6.5        | _         | )<br>18 Experiments                                         |

|   |            | 6.5.1     | Prerequisites                                               |

|   |            | 6.5.2     | Building Benchmark Binaries/Rootfses                        |

|   |            |           | Figure 5: Ping Latency vs. Configured Link Latency          |

|   | 6.6<br>6.7      | <ul> <li>6.5.5 Figure 7: Memcached QoS / Thread</li> <li>6.5.6 Figure 8: Simulation Rate vs. Scale</li> <li>6.5.7 Figure 9: Simulation Rate vs. Link</li> <li>6.5.8 Running all experiments at once</li> <li>GAP Benchmark Suite</li> <li>[DEPRECATED] Defining Custom Workload</li> <li>6.7.1 Uniform Workload JSON</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ation       10         Imbalance       10         Latency       10          10          10          10          10          10          10          10          10          10          10          10          10          10          10          10          10          10          10          10          10          10          10          10          10          10          10          10          10          10          10          10          10          10 <t< th=""><th>)3<br/>)4<br/>)4<br/>)4<br/>)5</th></t<> | )3<br>)4<br>)4<br>)4<br>)5                                                                                                                   |

|---|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 7 | Targ            | rgets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11                                                                                                                                           |

|   | 7.1             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                              |

|   |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                              |

|   |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                              |

|   | 7.2             | Target-Side FPGA Constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13                                                                                                                                           |

|   |                 | 7.2.1 RAM Inference Hints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13                                                                                                                                           |

|   | 7.3             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14                                                                                                                                           |

|   |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                              |

|   |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                              |

|   | 7.4             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | project)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                              |

|   |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                              |

|   |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                              |

|   | 7.5             | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | nory-Timing Model Instance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                              |

|   | 7.5             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                              |

|   | 7.6             | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                              |

|   | 7.0             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                              |

|   |                 | , and Emmipres                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                              |

| 8 | Debu            | bugging in Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                              |

| _ |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                              |

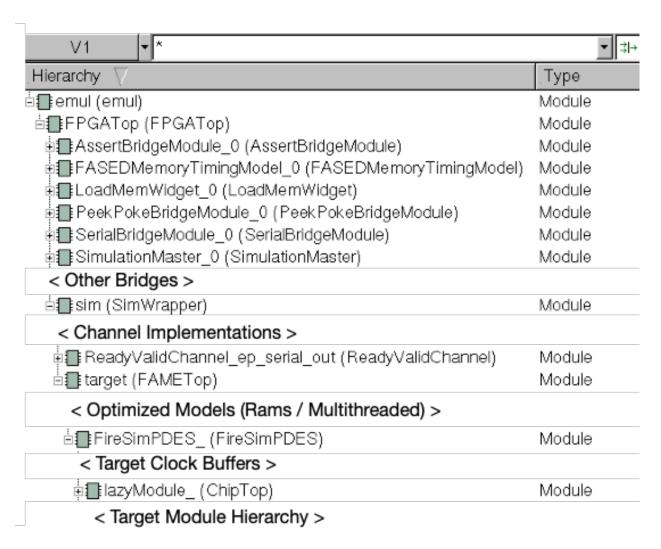

| _ | 8.1             | Debugging & Testing with Metasimulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                              |

| - |                 | Debugging & Testing with Metasimulation 8.1.1 Supported Host Simulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                                                                                                           |

| - |                 | Debugging & Testing with Metasimulation<br>8.1.1 Supported Host Simulators<br>8.1.2 Running Metasimulations using the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 19<br>20                                                                                                                                     |

| - |                 | Debugging & Testing with Metasimulation<br>8.1.1 Supported Host Simulators<br>8.1.2 Running Metasimulations using the<br>8.1.3 Understanding a Metasimulation W.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FireSim Manager         12           veform         12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19<br>20<br>21                                                                                                                               |